这样设计PCB中晶振电路减少问题

不管是产品选型,还是电路设计,对于工程而言总会遇到大大小小的问题,那么如何更好的设计PCB呢?这样设计PCB印刷电路板减少问题,在设计印刷电路板时,应考虑通过防止来抑制EMI水平负阻力下降.

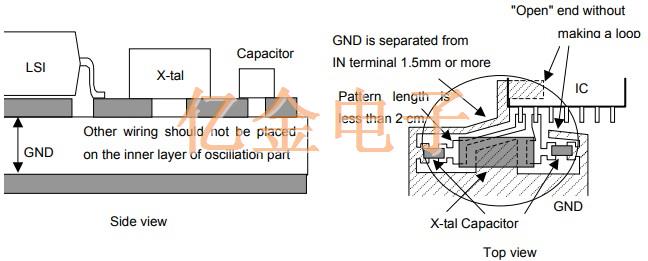

1.PCB上的图案长度

为了防止布线的电感和杂散电容导致电气特性的劣化,建议以最短的接线长度连接IC和电容器的石英晶体单元.这种模式长度应大约在2厘米以内,但长度越短,EMI辐射越小放置IC和晶体单元等元件不会成为问题.由于EMI主要来自于在逆变器的OUT侧,该部分的图形长度应该是晶体振荡电路中最短的.而且,插件晶振不是优选的,因为它们成为EMI的来源.

2.晶体振荡电路以外的图案的影响

在设计多层PCB的情况下,重要的是不设计场地或其他信号模式在图中圆圈部分的振荡电路下,以防止负电阻减小,并获得石英晶体振荡器稳定的启动特性.特别是,如果其他信号线位于靠近IN侧的位置振荡电路,振荡波形将被调制引起噪声,并在OUT侧放大成为EMI的原因.由于晶体振荡电路可能会停止启动,如果IN端子的电压和OUT端子在其他信号线的影响下变得相等,强烈建议不要设计它.还应该避免在振荡电路附近的层上放置场地,因为它会减少负面阻力很大.

3.用场地屏蔽

当用场地屏蔽时,它将被放置在距离元件侧最远的层上,如图所示左下图.接地图案不应放置在有源晶振,晶体振荡电路中以避免负电阻降低,并且其他信号线也不应该放在这个部分,因为它会调制振荡波形和通过降低负电阻来增加EMI.

如果元件上的有源晶振振荡电路的接地图案一侧靠近信号线放置,EMI水平会降低,但如果放得太近,它会减少负阻,建议将其与振荡电路的信号线分开0.5mm或更多.将接地图案设置得太靠近振荡电路的信号线是不利的,会降低负电阻,此外由于从IN辐射的EMI水平低,没有必要这样做.

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号