集成电路系统的平衡和低阻抗晶振的使用

随着专用集成电路的普及,其性能和速度也有了更高的限制,同时驱动多个设备变得更加困难,这是高性能系统目前的局限,所以我们需要一个强大的时钟晶振源来增强使用空间.但是由于快速边沿速率,系统中部署的较高频率导致长PCB迹线表现得像传输线.维护平衡系统需要适当的终止技术来实现应用程序中的跟踪路由.

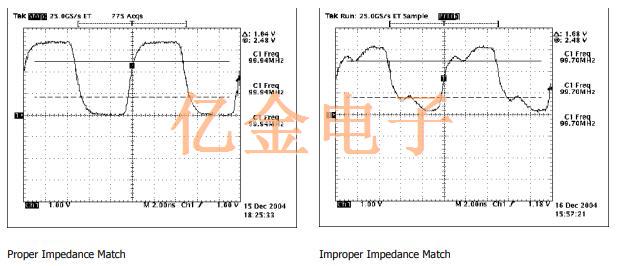

通常,大多数时钟晶振具有低阻抗输出。当这些器件用于驱动具有大阻抗的负载时,存在阻抗不匹配。根据应用条件,此阻抗不匹配会导致负载产生电压反射,从而在时钟波形,振铃以及过冲和下冲中产生步进。这可能通过降低负载处的时钟信号,错误的数据时钟和产生更高的系统噪声而导致系统性能不佳。

为了减少电压反射,需要正确终止信号迹线。适当终止的设计考虑因素可归纳为两个陈述:

1.将负载阻抗匹配到线路阻抗

2.将源阻抗与线路阻抗进行匹配

对于大多数设计,第一种说法是首选方法,因为它消除了返回时钟源的反射。这样可以减少噪音,电磁干扰(EMI)和射频干扰(RFI)。下图显示了阻抗不匹配对较高频率时钟源的影响。

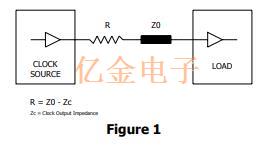

如上所述,为了减少电压反射,必须正确地终止迹线。传输线的四种基本端接技术是串联,并联,戴维南和AC。串联终端消除了时钟源的反射,四脚有源石英晶振有助于保持信号质量。这最适合驱动少量负载的TTL器件,因为时钟输出阻抗小于传输线特性阻抗。图1显示了一系列终端。电阻尽可能靠近时钟源放置。R的典型设计值为10Ω至75Ω。

R的值可以大于阻抗差,以便产生稍微过阻尼的状态并且仍然消除来自时钟源的反射。

系列终端的主要优点是:

1.简单,只需要一个电阻器

2.功耗低

3.驱动高容性负载时产生电流限制;这还可以通过减少接地反弹来改善抖动性能。

系列终止的主要缺点是:

1.增加负载信号的上升和下降时间;在某些高速应用中,这可能是不可接受的

2.无法驱动多个负载

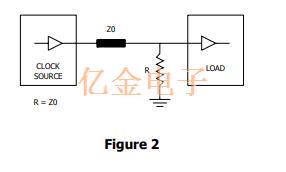

接下来的两种终端技术可提供更清晰的时钟信号,并消除负载端的反射。这些终端应尽可能靠近负载放置。图2描绘了并行终端。并联终端消耗的功率最大,不建议用于低功率应用。高精度贴片晶振也可能改变占空比,因为下降沿将比上升沿更快。它比串联终端具有一个优点,即上升和下降时间的延迟大约是一半。

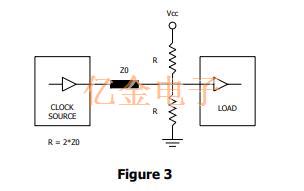

如图3所示,戴维南终端将比并联终端消耗更少的功率,并且通常用于PECL应用的50Ω线路匹配至关重要。R的总值等于传输线的特征阻抗。如果需要过阻尼条件,则R的总值可略小于特征阻抗。戴维南终端的主要缺点是每条线路需要两个电阻器,并且在终端附近需要两个有源晶振。不建议将此端接用于TTL或CMOS电路。

时钟晶振作为抵抗组输出的选择,维护系统平衡是主要任务之一,提供更清晰的时钟信号正是需要解决的问题,生成可靠的应用程序可以最大限度的降低时钟信号的条件,来保持系统性能的稳定

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号