艾尔西独家讲解振荡器的应用技巧及注意事项

艾尔西独家讲解振荡器的应用技巧及注意事项

如何正确了解石英晶体振荡器,如何运用振荡器,想必大多数人都会存有疑惑;本文正是就石英晶体振荡器的应用技巧进行介绍,并且其中还掺杂有在应用过程中的注意事项以及相关专业性知识解释,想要一解疑惑的朋友可以进来看一看.这篇文章是由美国艾尔西晶振公司发出的,觉得相当有讨论价值,与诸位共勉.

振荡器是产生连续输出信号的电路.因此它被称为信号发生器.当产生的信号是振幅和频率恒定的正弦波时,该振荡器电路称为正弦波发生器.该振荡器可以产生数字逻辑系列(如TTL,CMOS或ECL/PECL)中的方波信号.

振荡器可以分为三个确定的部分:

①放大器.

②反馈连接.

③频率确定组件.

④振荡要求

如果电路有两个最低要求,石英晶振将振荡:

①正反馈

②环路增益大于1

当我们将放大器的输出连接到其输入时,会提供反馈.如果反馈的输出与输入”异相”,则电路具有负反馈(NFB).如果来自输出的反馈与输入同相,则电路具有正反馈(PFB).

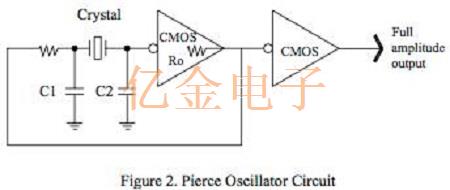

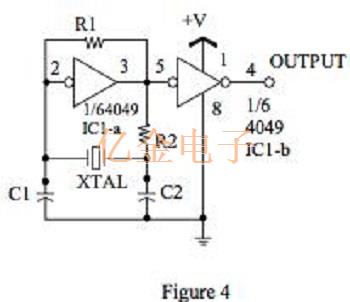

皮尔斯振荡器电路

优点:

①在串联谐振或串联谐振附近运行(从Fs大约为5ppm至200ppm).

②很好的短期稳定性.

③在1kHz至200MHz的任何频率下工作.

④电路提供较大的输出信号.

⑤以低功率驱动晶体.

⑥振荡频率几乎对串联.

电阻或并联电容的微小变化不敏感.

电路配置:

①在大多数Pierce电路中,放大器仅由一个晶体管组成.可以对输出进行缓冲,以提供数字逻辑兼容的输出(TTL或HC-CMOS)

②Pierce放大器可以设计成具有CMOS,TTL和ECL中的数字逻辑元件;CMOS用于低频,TTL用于中频和ECL用于高频.

晶体振荡器的三态控制

大多数数字系统使用由两个状态级别0和1表示的二进制数字系统.在某些特殊应用中,需要第三状态(HiImpedance输出).TTL,HCMOS或HCMOS石英晶体振荡器提供三态输出或三态启用/禁用功能.它的常见应用包括自动测试,总线接线数据传输.

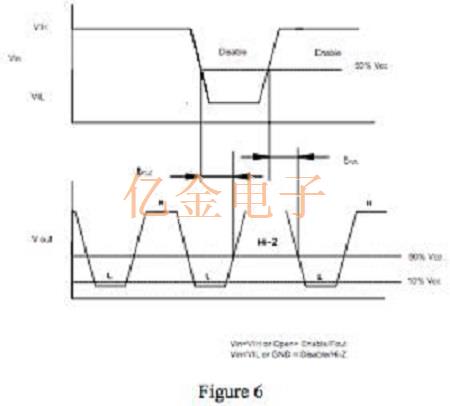

三种状态分别为低,高和高阻抗(HiZ或浮动).高阻抗状态下的输出的行为就好像它与电路断开连接一样,只是漏电流很小.三态设备具有启用/禁用输入,通常在几乎任何封装的引脚1上.当使能为高电平或悬空时,器件振荡(具有高和低输出),并且当引脚1接地(逻辑”0”)时,器件进入高阻态.

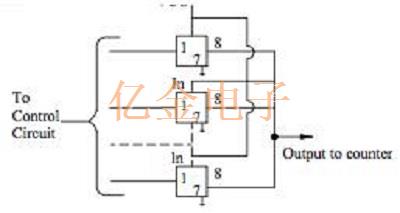

总线是一组常用的电线,通常用于数据传输.三态总线具有连接在一起的几个三态输出.通过控制电路,总线上除一个设备外的所有设备都具有处于高阻抗状态的输出.启用其余设备,以高和低输出驱动总线.

三态功能的其他应用是用于自动测试设备(ATE).几个有源贴片晶振的输出连接在一起.通过控制电路,除一个以外的所有振荡器都具有处于高阻抗状态的输出.唯一选择的振荡器将从计数器中读出其频率.(图5)

三态功能生效之前总会有一些延迟.在两个转换(禁用和启用)上都会发生这种效果.从低电平到三态的输出禁用时间为tPLZ,从低电平到三态的输出使能时间为tPZL.(图6)

CMOS

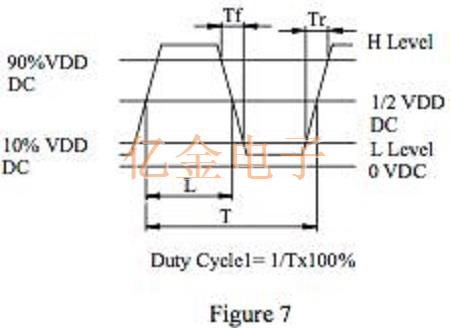

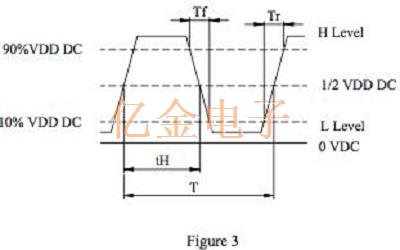

的上升和下降时间CMOS技术的上升和下降时间取决于其速度(CMOS,HCMOS,ACMOS,BICMOS),电源电压,负载电容和负载配置.CMOS40000系列的典型上升和下降时间为30ns,HCMOS为6ns,而ACMOS(HCMOS,TTL兼容)的最大上升时间为3ns.典型的上升和下降时间在其波形电平的10%至90%之间测量.(见图7)

ACMOS输出端接技术

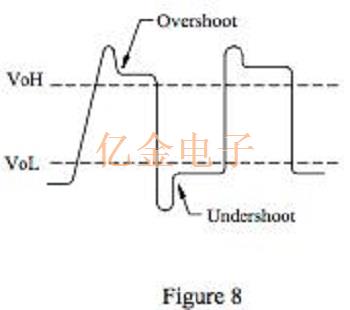

由于ACMOS(兼容HCMOS/TTL)器件的转换时间很快,因此在测试或测量电气性能特征时必须使用适当的端接技术.端接通常用于解决电压反射问题,电压反射问题实质上会导致时钟波形出现阶跃以及过冲和下冲.这可能导致错误的数据计时,以及更高的EMI和系统噪声.

由于PC板上走线的长度及其负载配置,也需要端接.终止时钟轨迹的一般方法有三种,这是将设备的输出阻抗与线路阻抗相匹配的过程:

方法1:串联端接在串联端接中,将阻尼电阻放置在靠近时钟信号源的位置.Rs的值必须满足以下要求:Rs≥ZT–Ro.

方法2:上拉/下拉电阻在上拉/下拉终端中,组合的戴维南等效值等于走线的特性阻抗.这可能是最干净的,不会产生反射,并降低了EMI.RT?ZT.

以上就是该文的全部内容,其中对石英振荡器的应用技巧进行了详细的说明,直至看完本文才知自己在这之前原来对有源晶振竟是仅知皮毛而已,本文对想要深入研究石英晶体振荡器以及设计晶体振荡器的朋友来说尤为珍贵,是一篇不可多得的技术性文章.

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号