当高频晶体振荡器信号彼此接近时,另外,串扰很可能会影响抖动每个输出的性能.了解如何放置输出时钟Si538x/4石英晶体振荡器上的引脚可实现最佳抖动和串扰性能.本应用笔记提供了Clock Builder Pro的“时钟放置向导”概述以及如何使用它来为您的频率计划和设备配置获得最佳的抖动和串扰性能.

1.晶体振荡器最低抖动和串扰的设计准则

在介绍“时钟晶体振荡器放置向导”如何工作以及如何使用它来实现特定有源晶体振荡器的最低抖动和串扰之前,Si538x/4x频率计划,请考虑以下输出时钟引脚配置准则.

1.1尽可能使用差分输出格式

为了获得最佳性能,强烈建议使用差分输出格式,例如LVDS,LVPECL,CML或HCSL.虽然晶体振荡器放置向导不会强制用户选择输出格式,建议使用差分输出,因为这些摆幅较低信令格式具有固有的平衡性,因此可以最大程度地减少共模噪声的产生.共模噪声通常是降低抖动性能和串扰的关键因素.相反CMOS输出振荡器是单端,摆幅轨到轨和具有亚皮秒的边缘速率.由于这些因素,CMOS输出振荡器会在以下情况下产生明显的单端电流浪涌:所有时钟晶体振荡器,因此会产生很大的串扰.由于这些原因,应在任何时候避免使用CMOS输出寻求低抖动性能时可能实现.如果必须在频率计划中使用CMOS输出,则最好放置此输出尽可能远离其他时钟,中间使用未使用的输出.输出格式可以轻松地在Clock Builder Pro配置向导.

1.2小心放置时钟销

Clock Placement Wizard(时钟晶体振荡器放置向导)将分析所有晶体振荡器输出,并安排它们,以避免放置会引起抖动的晶振,集成带宽彼此相邻.常用的集成带宽是12kHz至20MHz. ClockPlacement向导在其算法中使用此带宽.如果两个有源晶振,晶体振荡器输出之间的间隔接近20MHz输出频率,这可能会导致串扰问题.

例如,如果振荡器2为155.52MHz,振荡器3为156.25MHz,则156.25MHz–155.52MHz=730kHz.由于730kHz在12kHz至20MHz的集成带宽内,因此CPW的自动放置算法假设有更好的选择,我们尝试找到一种避免将这两个振荡器相互放置的方法.这两个输出信号将如果并排放置,则会在730kHz和730kHz的倍数处产生杂散,这些杂散将在12kHz至20MHz的积分频带内.这些杂散会导致更高的抖动.如果有未使用的时钟输出,最好在两个晶体振荡器之间有一个未使用的时钟输出在此示例中,晶振2和晶振3.此外,晶振2和晶振3应该与其他更高频率放置在更远的地方它们之间的差距要大得多,并且超出了集成范围.

请注意,积分带宽接近度放置算法不适用于彼此简单整数倍的晶体振荡器.例如,即使10MHzx2=20MHz和20MHz,也可以将20MHz振荡器和10MHz振荡器彼此并排放置.MHz–10MHz=10MHz,两者都位于积分频带内.简单整数关系不是问题的原因这是因为一个时钟的边沿不相对于另一时钟的边沿移动.时钟放置向导将全部考虑在内.

1.3考虑降低输出摆幅和I/O电压

如果使用时钟晶体振荡器放置向导无法获得最佳性能,并且您的设计中包含了AN862手动引脚放置的详细信息,则可以通过使用较低的I/O电压(2.5或1.8V)来改善差分晶振,晶体振荡器抖动性能.用于CMOS和/或定制的低摆幅差分输出信号设置.

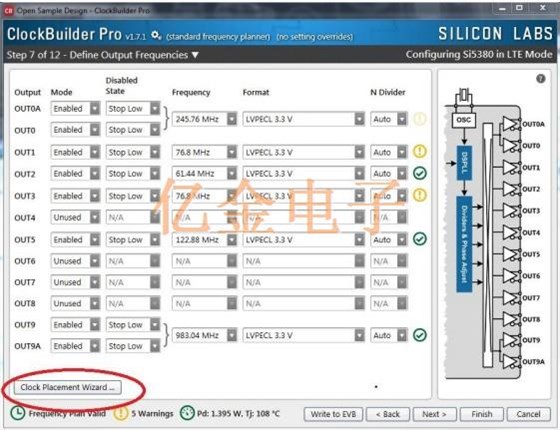

2.使用时钟晶体振荡器放置向导在“定义输出频率”菜单步骤中访问“时钟放置向导”,如下所示.请注意,此示例频率计划的某些输出旁边当前有警告符号.这些警告表明输出位置尚未针对抖动和串扰进行优化.

图2.1.定义的输出频率,访问时钟晶体振荡器放置向导

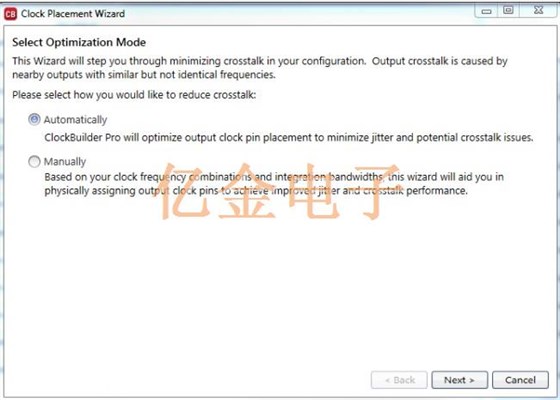

单击“时钟放置向导”按钮,出现两个选项:

1.自动优化输出时钟放置,以运行自动放置算法.

2.手动优化输出时钟位置,从而可以快速重新排列输出顺序.

图2.2.选择时钟晶体振荡器放置的优化模式

3.结论

通过遵循本应用笔记中描述的准则,并使用时钟晶体振荡器放置向导,可以快速轻松地实现Si534x/8x系列抖动振荡器和时钟晶体振荡器的最佳抖动和串扰性能.

SMI晶振,86M0368 -16,86SMX进口晶振,6G相关设备晶振

SMI晶振,86M0368 -16,86SMX进口晶振,6G相关设备晶振 日本SMI晶体,53SMX石英晶振,53M320-16,6G基站晶振

日本SMI晶体,53SMX石英晶振,53M320-16,6G基站晶振